ルネサスのWEBセミナーでAD変換の精度を良くする方法のセミナーがあったので、内容をちょっとご紹介。

といっても、さほどトリッキーな話はでてこないので、普段から設計している人なら「なーんだそんなこと」かもしれません。

それでも一応紹介します。

1,サンプル時間を長くする

2,外付け抵抗を小さくする

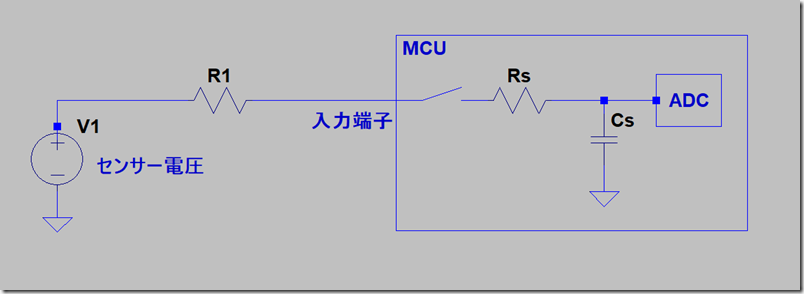

マイコンのAD変換回路の前段にサンプルホールド回路という物が内蔵されています。

中身は単純で、スイッチとコンデンサがセットになった物。

外部の電圧をいったんコンデンサにチャージしてからAD変換にかけます。

つまり、外部の電圧とこのコンデンサの電圧をきっちりあわせないと正確なAD変換になりません。

この電圧をきっちりあわせる一つ目の方法はサンプル時間を長くすること。

サンプル時間を長くすると言うのは、スイッチを入れておく時間を長くして時間をかけてチャージをかけると言うこと。

マイコンによって調整できたりできなかったりします。

チャージする時間が短すぎると内部コンデンサの電圧が上がりきるor下がりきる前にスイッチが切れてしまうので、変な値になってしまいます。

次に外付け抵抗R1を小さくすること。

ここで「外付け抵抗」と言っていますが、実際にはマイコンのADポートから見たものなので、目に見える抵抗がなくてもセンサーの内部抵抗も外付け抵抗と同じになります。

アナログセンサーだと内部抵抗が大きい部品も結構ありますからね。

ルネサスでは以下の式を満たす定数にしろとのことでした。

サンプル時間>定数×Cs(Rs+R1)

| 分解能 | 定数 |

| 8bit | 6 |

| 10bit | 8 |

| 12bit | 9 |

この定数はルネサスの特定のCPUの場合なので、別のCPUでは変わると思います。

しかし、考え方は共通です。

ただ……世の中の普通のマイコン(TIとかSTMicroとかもろもろ)は、AD変換部のサンプリングホールド用のコンデンサの容量・抵抗の値なんてデータシートに書いてありません。

分解能と精度と入力電圧範囲外の仕様が全く公開されていないという酷いCPUだってあります。(しかもAD変換部の詳細仕様を問い合わせても「ない」で終わったりする)

問い合わせて分かるようであれば上記の式で目安が出せますが、出ないばあいはできる限り外付け抵抗を小さくしてサンプリング時間をとるしかありません。

最後はデバッグでサンプリング時間をいじって様子を見るしかないかもしれません。

3,コンデンサをつける

外付け抵抗が大きくて内部コンデンサになかなか充電されない場合は、ADC入力端子に外付けコンデンサをつけます。

これにより外部コンデンサ→内部コンデンサに電流が流れるので、高速で内部コンデンサに充電されるようになります。

遅い信号に限りますが、ADC入力端子にコンデンサをつける手は実際に結構使われます。

ただ、外付けコンデンサが小さいと内部コンデンサに電荷が移動した際に電圧が下がってしまうので、外付けコンデンサは内部コンデンサよりも大分大きい必要があります。

具体的には、

C1 > 2^n × Cs

を満たす必要があります。

つまり、10bitなら内部コンデンサの1024倍、16bitなら内部コンデンサの65536倍の容量のコンデンサをつける必要があります。

でないと精度がおちます。

4,AD変換時にマイコンに大電流を流さない

マイコン自体に大きな電流が流れていると、VCCやGNDの微少な抵抗成分によって、VCCとGNDの電圧がずれてしまいます。

それが原因となって精度が悪化します。

ということで可能な限りマイコンの消費電流を抑えた方が精度がよくなります。

クロックを落とすとか、LEDを直接駆動しないとか。

5,AD変換する信号の近くに高速信号を通さない

これは当たり前ですね。

隣の端子や併走する配線に高周波が乗っていればクロストークで乗ってきてしまうのでSN比が悪化します。

6,VREF-GND間にコンデンサをつける

これもわりと当たり前ですが、ちゃんとつけましょうって話です。

VREFがずれるとAD変換の結果もずれてしまうので。

というところでした。

最近のコメント